HBM차세대 메모리의 설명에 앞서 컴퓨터의 구조를 먼저 설명합니다.

컴퓨터의 연산처리구조

사용자가 컴퓨터에 A라는 단어(신호)를 입력한다고 하면 해당 신호는 CPU에 의해서 각 장치에 명령이 전달됩니다.

CPU는 디스플레이 컨트롤러에게 A라는 단어를 표시하게 하고 우리는 그것을 모니터로 확인하게 됩니다.

이렇게 간단한 연산의 경우에는 문제가 되지 않지만, Chat GPT등 인공지능으로 많은 데이터를 검색하고 표현해야하는 그래픽처리를 위해서는 빠른 연산이 필요한 메모리가 필요합니다.

처리속도의 지연을 Bandwidth라고 이야기하며, 이는 CPU와 메모리(stotage)의 속도차이라고 합니다.

해결방법으로는 대역폭 메모리를 사용하게 되었고 우리가 흔히 알고있는 DRAM을 적용햐여 DDR이라는 표준을 만들었습니다.

그래픽부분의 대역폭 메모리인 GDDR을 사용하고 있으나, 인공지능과 결합된 더 빠른속도의 처리에 한계를 보였습니다.

그래서 등장한 기술이 HBM (High Bandwidth Memory)입니다.

HBM (High Bandwidth Memory)이란 무엇인가?

아래 그림을 설명하겠습니다.

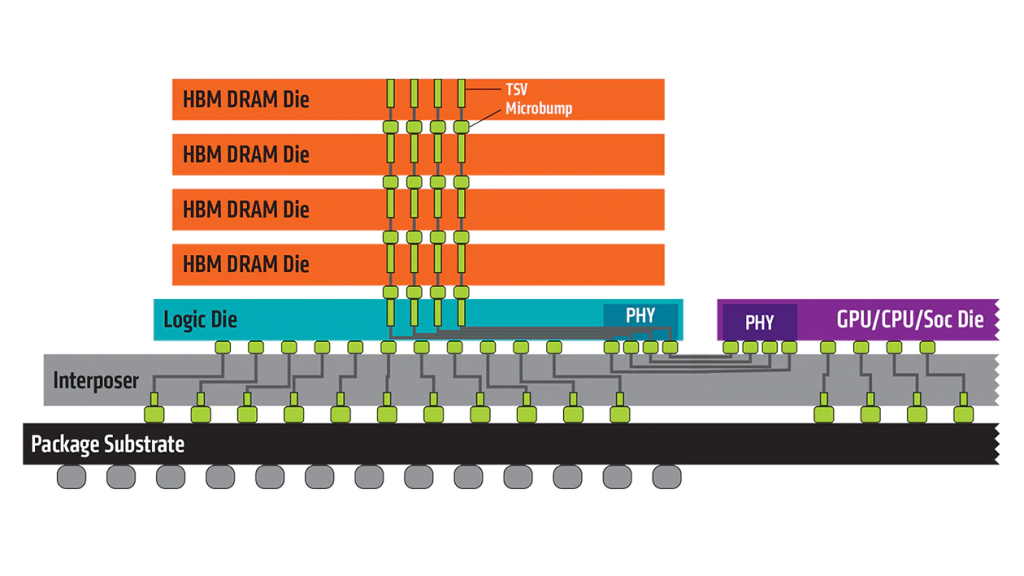

메모리를 와이어로 병렬연결을 하는것이 칩을 여러 개 쌓고 가운데 구멍을 뚫어 서로 연결하는 기술입니다.

HBM은 3D적층기술을 기반으로 칩간격마다 빠른 데이터이동을 위한 데이터 이동통로 –TSV(Through Silicon Via)라는 공정을 사용

높은 대역폭의 이동과 낮은 전력소비의 장점, 수직구조의 공간최소화를 이루어냈습니다.

수평구조의 메모리보다 적층구조의 논리회로 최적화로 인하여 전력효율성을 높혀 발열을 제어하는 장점이 있습니다.

출처 : techinsights

아파트로 비교한다면 같은 땅에 높은 고층아파트를 건축해서 많은 입주자들이 들어간다는 개념으로 생각하고 그 안에서 모든 생활이 이루어진다고 생각하는것이 합리적인 비교입니다.

HBM에서의 3D적층구조 설명

해당기술은 반도체 설계회사들의 미래경쟁으로 돌입하였다

삼성전자, 하이닉스가 기존 반도체의 장점을 살려서 현재 시장의 주 공급을 진행중이고, 인텔,TSMC등 다른 기업들도 협력을 해서 진행중이다.

그렇다면 3D적층기술에 대해서 살펴보겠습니다.

반도체 성능을 높이고 면적을 줄이려면 반도체 내부의 회로 폭을 미세화하기위해 현재 극자외선(EUV) 첨단 노광 공정으로 수나노미터급 회로 구현을 성공하여 생산공정에 적용하고 있습니다.

*EUV공정이란? 반도체 웨이퍼에 메모리 설계를 위한 미세한 설계도를 그려야합니다. 이러한 공정을 노광공정이라고 하고, 극자외선을 사용하여 빛의 굴절을 최소화하여 진행하고 있는 첨단공정입니다.

3D 적층 방식은 성능 고도화뿐 아니라 반도체 집적도를 높일 대안으로 주목받는다. 횡 방향(2D)이 아닌 위로 반도체를 쌓아 올려 점유 면적을 최소화할 수 있기 때문이다. 적층뿐 아니라 여러 반도체 기능을 하나의 칩으로 구현하는 칩렛도 차세대 패키징 기술로 떠오른다.

TSMC는 AMD 데이터센터 중앙처리장치(CPU)에 3D 패키지 기술 ‘3D SoIC(System on Integrated Chip)’를 적용했다. 이 기술은 고성능 반도체칩(다이) 위에 캐시 메모리를 완전히 포개어 붙였다.

3D SoIC는 칩을 적층하면서 칩 간 간격을 최소화할 수 있는 하이브리드 본딩을 적용했다. 마이크로 범프로 연결할 때보다 전기 전달 속도를 높일 수 있다.

인텔은 차세대 포베로스 기술개발을 진행중이다. 구리 다이렉트 본딩 방식으로 적층하는 칩 간 간격을 최소화하는 것이 목표다.

삼성전자는 2018년 고대역 반도체(HBM)와 로직 반도체를 집적한 아이큐브를 선보였고, 지난해 로직 반도체와 캐시 메모리를 수직으로 쌓아 올리는 엑스큐브 3D 적층 기술을 공개했다.

HBM 등 고대역 반도체칩을 더 많이 탑재하면서 매우 얇은 인터포저가 변형되지 않으면서 초미세 배선을 구현할 수 있도록 했다.

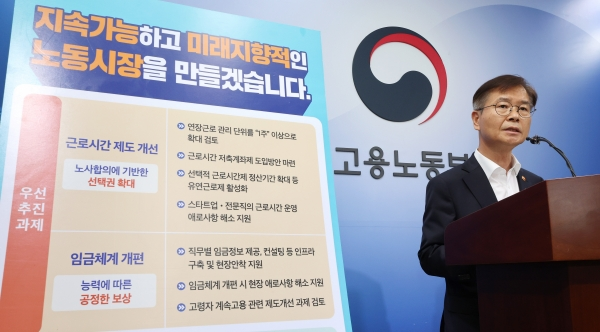

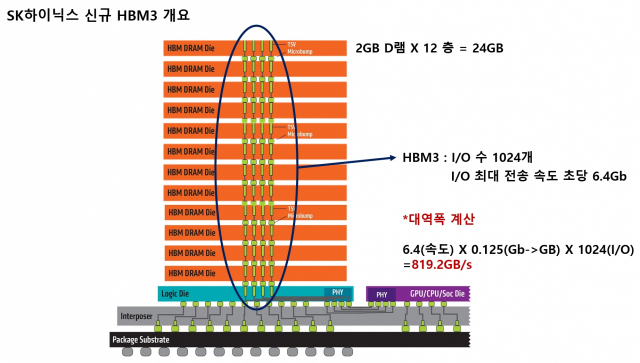

현재 시장의 주도권은 하이닉스에서 엔비디아에 HBM3(현존 최고사양의 D램)을 공급하면서 앞서나가는 현실이다.

엔비디아의 H100 GPU와 결합하여 AI기반으로 사용될 예정이라고 합니다.

* HBM(High Bandwidth Memory): 여러 개의 D램을 수직으로 연결해 기존 D램보다 데이터 처리 속도를 혁신적으로 끌어올린 고부가가치, 고성능 제품. HBM3는 HBM 4세대 제품으로, HBM은 1세대(HBM)-2세대(HBM2)-3세대(HBM2E) 순으로 개발돼 왔음. SK하이닉스의 HBM3는 FHD(Full-HD) 영화 163편을 1초에 전송하는, 최대 819GB/s의 속도를 구현함

출처 : https://news.skhynix.co.kr/presscenter/mass-production-of-hbm3-dram

DRAM별 전송속도와 대역폭을 설명합니다.

현재 HBM의 경우 차세대 메모리로 분류되는 이유가 설명됩니다.

CPU와 GPU의 차이는 무엇일까?

CPU의 경우 직렬연산으로 명렬어른 한번에 하나씩 순서대로 처리하는 방식입니다.

인공지능이 결합된 경우에는 한번에 많은양의 데이터 처리가 필요하므로 CPU보다는 병렬연산(동시에 많은 연산을 수행해 속도를 높임)의 GPU(그래픽처리장치)가 적합합니다.

GPU는 AI데이터 센터등 대용량 서버에서 사용되기 적합하다고 이해하면 됩니다.

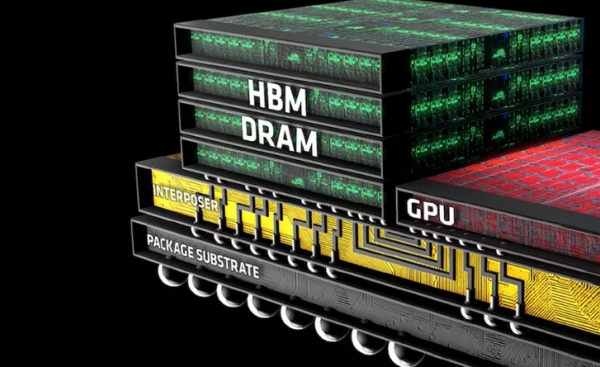

GPU와 HBM의 구조에 대해서 설명

출처 : 엔비디아 홈페이지

GPU의 구성입니다. 중앙에 GPU칩을 중심으로 GDDR의 구성으로 되어있습니다.

여기에서 GDDR의 차세대 구조인 HBM을 적용하면 다음과 같은 구성입니다.

GDDR대비 사용공간의 효율성(공간의 최소화)으로 발열을 낮추고 병렬연결을 수직구조화하여

데이터 처리속도를 증가시키는 구조라고 이해하면 됩니다.

SK하이닉스 GDDR6(2GB/s 속도 기준) 제품 12개와 HBM3 4개 대역폭을 비교하면 GDDR6 속도(초당 3GB)대비 3배 증가됩니다.

출처 : https://www.sedaily.com/NewsView/29OEGJGUPB

마무리(세특콘텐츠 추천)

수험생의 세특주제로 사용가능한 부분을 정리해봅니다.

물리에서의 빛과 파동부분에서 전자기파를 확대하여 메모리 안의 전자이동을 연결해서 심화탐구가 가능합니다.

키르히호프의 전류법칙, 전압법칙 (KCL, KVL)의 기본구조를 한번더 설명하여 실제 사용되는 라디오, 스피커의 구조를 기하와 연결하여 설명도 가능하겠네요

추가적으로 반도체공정 (삼성반도체 홈페이지 참고)하여 노광공정에서 사용되는 기술을 탐구해보는것도 좋습니다.

반도체업계에서는 HBM이라는 기술을 메모리를 넘어서 트랜지스터까지 적층구조를 준비하는 신기술이 진행되고 있습니다.

초전도체에 밀려서 이러한 기술이 많은 노출이 되지 않는것을 감안하더라도 획기적인 기술이며, 미래의 기술이 아닌 현재 개발해서 생산하는 기술이기에 충분한 콘텐츠가 될 것이라고 생각됩니다.

물리2, 고급물리, 융합과제등 다양한 공대생들의 과제로 컴공, 반도체학과, 시스템학과를 지망하는 학생들이 사용하시길 바랍니다.

https://news.skhynix.co.kr/presscenter/mass-production-of-hbm3-dram